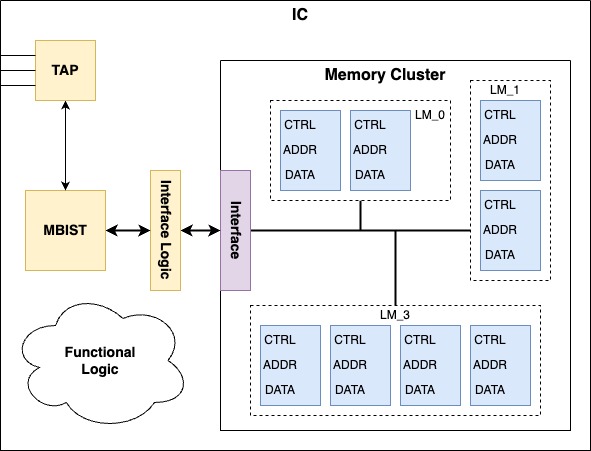

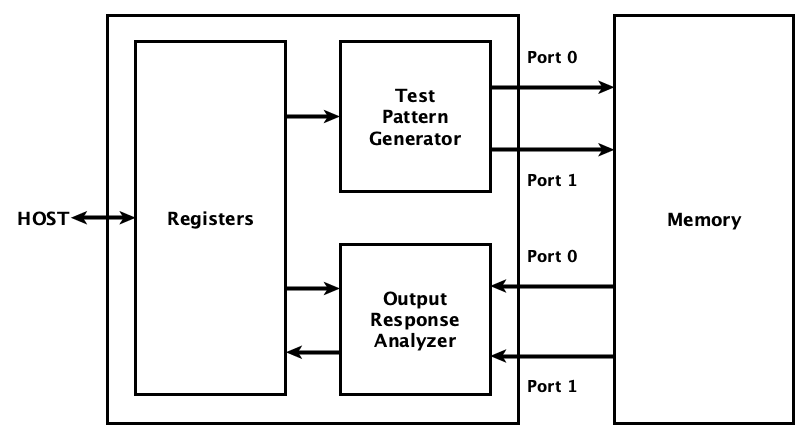

Memory Built-In Self Test (MBIST) design used for automatic fault detection in single-port as well as dual-port SRAM memories. Intended for implementation as part of ASIC (Application-Specific Integrated Circuit) designs. Developed as part of the Master’s Thesis. Implemented in Verilog HDL.

| Language | Verilog |

| Tools | ModelSim, Icarus Verilog, GTKWave, Xilinx ISE |

| Target | ASIC, Virtex 6 (tests) |

| Time frame | 12.2017 – 02.2019 |

| Commercial | ✔ |

| Collaboration | ChipCraft – verification in FPGA and utilisation in ASIC |

Introduction to MBIST

Most of currently used digital systems (such as processors) utilize memories. In many cases these memories occupy a significant part of integrated circuit area. In order to efficiently verify, if each memory cell is working as expected (not introducing faults), a specialized MBIST block is implemented and used. These kind of blocks are implemented in every modern, more complex digital integrated circuits (including processors), but most of the time the end user has no access to it.

Additionally, a dedicated MRAM controller enables memory verification not only immediately after production, but during system maintenance procedures as well. This is another reason why this type of blocks are used instead of other types of verification. The defects can occur due to aging processes as well.

Together with MBIST block, a behavioral dual-port memory model with random delays and SRAM faults simulation was implemented for verification purposes.

Selected features of the implemented MBIST

- Single-port and dual-port memory support

- Support for direct memory connection as well as through a system bus

- Option to implement only selected memory testing algorithms – separately for each MRAM instance

- A single MBIST block can support multiple memories with different features (i.e. word width, depth etc.)

- By default 7 single-port and 2 dual-port memory tests implemented – including algorithms widely used in the industry

- Easy to implement new testing algorithms – including for other memory types than SRAM

Implemented SRAM testing algorithms:

| Lp. | Nazwa testu | Złożoność testu | Algorytm |

| 1 | Zero-one | 4n | {⇕(w0); ⇕(r0); ⇕(w1); ⇕(r1)} |

| 2 | Checkerboard | 4n | {⇕(w10, w01); ⇕(r10, r01); ⇕(w00, w11); ⇕(r00, r11)} |

| 3 | MATS | 4n | {⇕(w0); ⇕(r0, w1); ⇕(r1)} |

| 4 | MATS+ | 5n | {⇕(w0); ⇑(r0, w1); ⇓(r1, w0)} |

| 5 | March X | 6n | {⇕(w0); ⇑(r0, w1); ⇓(r1, w0); ⇕(r0)} |

| 6 | March C | 11n | {⇕(w0); ⇑(r0, w1); ⇑(r1, w0); ⇕(r0); ⇓(r0, w1); ⇓(r1, w0); ⇕(r0)} |

| 7 | March C- | 10n | {⇕(w0); ⇑(r0, w1); ⇑(r1, w0); ⇓(r0, w1); ⇓(r1, w0); ⇕(r0)} |

| 8 | March s2PF | 14n | {⇕(w0 : n); ⇑(r0 : r0, r0 : –, w1 : r0); ⇑(r1 : r1, r1 : –, w0 : r1); ⇓(r0 : r0, r0 : –, w1 : r0); ⇓(r1 : r1, r1 : –, w0 : r1); ⇓(r0 : –)} |

| 9 | March d2PF | 9n | {⇕(w0 : n); ⇑C-1c=0 (⇑R-1r=0 (w1r,c : r0r+1,c)); ⇑C-1c=0 (⇑R-1r=0 (w1r,c : r1r+1,c)); ⇑C-1c=0 (⇑R-1r=0 (w0r,c : r1r+1,c)); ⇑C-1c=0 (⇑R-1r=0 (w0r,c : r0r+1,c)); ⇑C-1c=0 (⇑R-1r=0 (w1r,c : r0r,c+1)); ⇑C-1c=0 (⇑R-1r=0 (w1r,c : r1r,c+1)); ⇑C-1c=0 (⇑R-1r=0 (w0r,c : r1r,c+1)); ⇑C-1c=0 (⇑R-1r=0 (w0r,c : r0r,c+1))} |

References

- A. A. Wojciechowski, K. Marcinek and W. A. Pleskacz, „Configurable MBIST Processor for Embedded Memories Testing,” 2019 MIXDES – 26th International Conference „Mixed Design of Integrated Circuits and Systems”, Rzeszów, Poland, 2019, pp. 341-344.

- Said Hamdioui, J. van de Goor, “Efficient Tests for Realistic Faults in Dual-Port SRAMs,” IEEE TRANSACTIONS ON COMPUTERS, vol. 51, no. 5, 2002.

- Said Hamdioui, Testing Static Random Access Memories: Defects, Fault Models and Test Patterns. Springer Science+Business Media, LCC, 2004.